8051 has 128K bytes of address space of which 64K bytes are set aside for program code and the other 64K bytes are set aside for data. Program space is accessed using the program counter (PC) to locate and fetch instructions, but the data memory space is accessed using the DPTR register and an instruction called MOVX, where X stands for external.

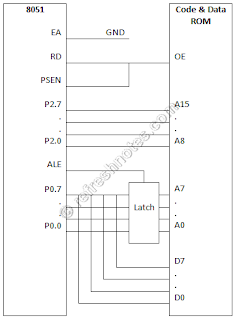

External Data ROM:

To connect the 8031/51 to external ROM containing data, we use RD. For the ROM containing the program code, PSEN is used to fetch the code. For the ROM containing data, the RD signal is used to fetch the data.

MOVX is a widely used instruction allowing access to external data memory space. To bring externally stored data into the CPU, we use the instruction “MOVX A, @DPTR”. This instruction will read the byte of data pointed to by register DPTR and store it in the accumulator. In writing data to external data RAM, we use the instruction “MOVX @DPTR, A” where the contents of register A are written to external RAM whose address is pointed to by the DPTR register.

Read from External Data ROM:

Copy from External Data ROM to Internal RAM:

8051 with External Data and Program ROM:

Single External ROM for Program and Data:

A single external ROM chip is used for both program code and data storage. The space 0000H – 7FFFH is allocated to program code, and address space D000H – FFFFH is set aside for data. In accessing the data, we use the MOVX instruction. For accessing code, we use MOVC instruction.

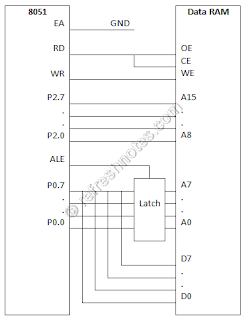

External Data RAM:

Read data from Port1 and store in external RAM:

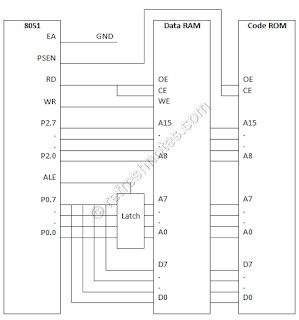

External ROM and RAM:

Memory more than 64KB:

In some applications we need a large amount (256K. bytes, for example) of memory to store data. However, the 8051 can support only 64K bytes of external data memory since DPTR is 16-bit. To solve this problem, we connect A0 – A15 of the 8051 directly to the external memory’s A0 – A15 pins, and use some of the PI pins to access the 64K-byte blocks inside the single 256Kx8 memory chip.

External Data ROM:

To connect the 8031/51 to external ROM containing data, we use RD. For the ROM containing the program code, PSEN is used to fetch the code. For the ROM containing data, the RD signal is used to fetch the data.

MOVX is a widely used instruction allowing access to external data memory space. To bring externally stored data into the CPU, we use the instruction “MOVX A, @DPTR”. This instruction will read the byte of data pointed to by register DPTR and store it in the accumulator. In writing data to external data RAM, we use the instruction “MOVX @DPTR, A” where the contents of register A are written to external RAM whose address is pointed to by the DPTR register.

Read from External Data ROM:

ORG 0H MYDATA EQU 1000H COUNT EQU 30 MOV DPTR, #MYDATA ; point to data in external data ROM MOV R2, #COUNT AGAIN : MOVX A, @DPTR MOV P1, A INC DPTR DJNZ R2, AGAIN END

Copy from External Data ROM to Internal RAM:

ORG 0H TABLE EQU 000H RAMTABLE EQU 30H COUNT EQU 10 MOV DPTR, #TABLE ; point to data in external data ROM MOV R5, #COUNT MOV R0, #RAMTABLE AGAIN : MOVX A, @DPTR MOV @R0, A INC DPTR INC R0 DJNZ R5, AGAIN END

8051 with External Data and Program ROM:

Single External ROM for Program and Data:

A single external ROM chip is used for both program code and data storage. The space 0000H – 7FFFH is allocated to program code, and address space D000H – FFFFH is set aside for data. In accessing the data, we use the MOVX instruction. For accessing code, we use MOVC instruction.

External Data RAM:

Read data from Port1 and store in external RAM:

ORG 0H RAMDATA EQU 5000H COUNT EQU 200 MOV DPTR, #RAMDATA ; point to data in external RAM MOV R3, #COUNT AGAIN : MOV A, P1 MOVX @DPTR, A ACALL DELAY INC DPTR DJNZ R3, AGAIN HERE : SJMP HERE DELAY : MOV R5, 255 LOOP : DJNZ R5, LOOP RET END

External ROM and RAM:

Memory more than 64KB:

In some applications we need a large amount (256K. bytes, for example) of memory to store data. However, the 8051 can support only 64K bytes of external data memory since DPTR is 16-bit. To solve this problem, we connect A0 – A15 of the 8051 directly to the external memory’s A0 – A15 pins, and use some of the PI pins to access the 64K-byte blocks inside the single 256Kx8 memory chip.

Related topics:

8051 External Program Memory Interfacing | 8051 Memory Mapped IO | 8051 LED Interfacing | 8051 Switch Interfacing | 8051 Keyboard Interfacing | 8051 7-Segment Display Interfacing | 8051 LCD Interfacing | 8051 ADC Interfacing | 8051 DAC Interfacing | 8051 Relay Interfacing | 8051 Sensor Interfacing | 8051 Stepper Motor Interfacing | 8051 DC Motor Interfacing

List of topics: 8051

Thank you Kathireshan Ganesan for the in depth explanation

ReplyDeleteIn order to avoid potential problems, most companies have adopted an all inclusive data storage approach, holding onto all data that flows through the company. Self Storage

ReplyDelete